分項計畫1 新穎材料 (奈米膜工程與元件、二維材料)

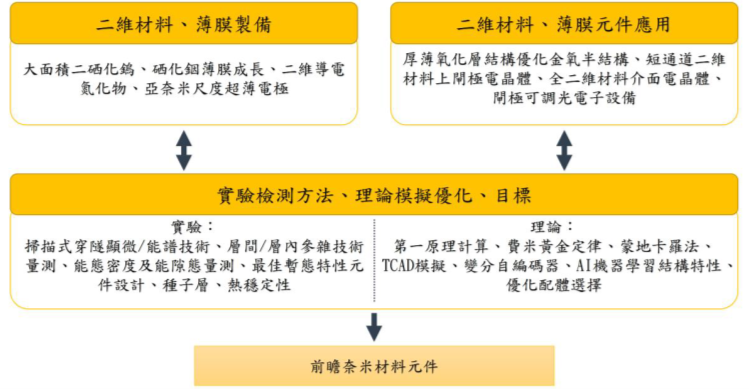

本分項致力於研發與優化前瞻二維場效電晶體元件開發,並由場效電晶體之基礎架構分四大方向進行團隊合作,分別對於金氧半穿隧二極體、上閘極 N/P型二維材料電晶體與接觸摻雜技術 、多層二維材料、發展功函數可調之導電氮化物,作為超薄閘極電極、掃描穿隧能譜檢測技術與元件效能模擬等方面進行技術開發與探討。

金屬閘極在場效電晶體元件架構中是非常重要的組成要件,研發超薄型閘極電極材料為發展未來場效電晶體元件的關鍵議題。因此,本分項1將開發導電氮化物作為超薄閘極電極解決薄金屬之導電性能與界面相容性等問題。團隊也將提出利用特殊設計的氧化層厚薄組合,於超薄氧化層金氧半穿隧二極體元件於偏壓切換時,調控少數載子因分布不均勻引起額外的暫態特性,作為記憶元件相關應用。

同時,也期望能透過近期蓬勃發展的機器學習技術,探索材料設計的相關應用,並以自組裝單分子層和選擇性沉積為核心技術。因此,探索機器學習在分子設計的應用,可說是實現快速開發新材料的關鍵契機。

二維材料次奈米世代的元件架構,除目前使用之閘極全環電晶體架構設計技術(GAA-FET) 外,以其他新穎材料取代傳統矽材料做為通道層的電晶體架構設計也被視為可延續摩爾定律(Moore's Law) 的關鍵研發方向。對此,分項1將對於上閘極N與P型二維場效電晶體進行開發,以降低元件的次臨界擺幅(subthreshold swing) 與等效二氧化矽厚度(equivalent oxide thickness, EOT) 為主要目標,改善二維材料與high k material接面缺陷的問題,開發高效能的二維材料電晶體元件。

隨著低維度材料整合的製備與技術日益發展,對於全二維材料組成的金屬─半導體同質介面(homojunction) 結構的介面物理機制,仍缺乏合適的微觀探測技術,因此本分項將開發金屬-半導體介面奈米尺度量測技術,以釐清低維度的金屬─半導體同質介面中的關鍵電子傳輸特性。最後,結合第一性原理模擬與蒙地卡羅的計算方法,模擬二維材料的電子性能以找出適切的通道候選材料,並對上下閘極等電晶體結構對於電晶體元件表現的影響進行測試,探討其臨界擺幅(Subthreshold Swing, SS) 與二氧化矽厚度差異。